Page 20 - 電路板季刊第109期

P. 20

18 專業技術 先進封裝與銅銅對接(2) Advanced Package

2.16 ආSiPӻ୕܆ༀၾCoWoS-Sݴື(7)

2.16 先進SIP系統封裝與CoWoS-S流程細節(7)

封

裝

與

統

先

進

系

細

節

流

程

Hybrid Bonding

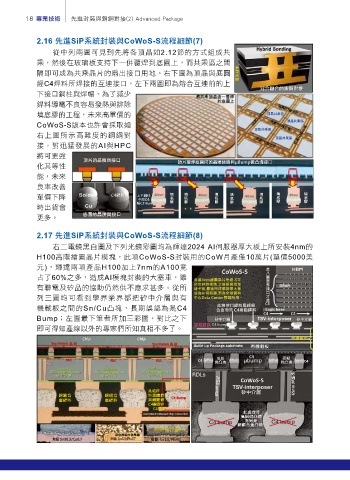

從中列兩圖可見到先將各頂晶如2.12節的方式組成共

從中列兩圖可見到先將各頂晶如2.12節的方式組成共乘,然

乘,然後在玻璃板支持下一併覆焊到底圓上,而共乘區之間 無需底膠

後在玻璃板支持下逐一覆焊到底圓上,而共乘區之間隔即

可成為共乘晶片的扇出接口用地。右下圖為頂晶與底圓經

隔即可成為共乘晶片的扇出接口用地。右下圖為頂晶與底圓

C4焊料所焊接的互連接口,左下兩圖即為熔合互連前的上

經C4焊料所焊接的互連接口,左下兩圖即為熔合互連前的上 混合鍵合的銅銅對接

下接口銅柱與焊帽。為了減少焊料導電不良容易發熱與排

除填底膠的工程,未

下接口銅柱與焊帽。為了減少 將共乘

來高單價的CoWoS-S版

銲料導電不良容易發熱與排除

本也許會採取如右上圖

填底膠的工程,未來高單價的 頂晶共乘區

所示高難度的銅銅對

接,對迅猛發展的AI與

CoWoS-S版本也許會採取如 頂晶共乘區

HPC將可更強化其等性 頂晶共乘區

右上圖所示高難度的銅銅對 頂晶共乘區

能,且良率改善單價

接,對迅猛發展的AI與HPC

下降出貨會更多。

將可更強

頂片覆焊底圓時的晶臉線路與μBump微凸塊接口

化其等性

能,未來

良率改善

填底膠 填底膠 填底膠 填底膠 填底膠 填底膠 填底膠

單價下降 C4銲料 上下銅柱 40nm 40nm 40nm 40nm

中間C4

稱C2 Bump

時出貨會

更多。 底圓的晶臉與接口

2.17 ආSiPӻ୕܆ༀၾCoWoS-Sݴື(8)

右二電鏡黑白圖及下列光鏡彩圖均為輝達2024 AI伺服器厚大板上所安裝4nm的

2.17 先進SIP系統封裝與CoWoS-S流程細節(8)

裝

封

細

節

程

與

流

統

進

先

系

H100高階繪圖晶片模塊,此項CoWoS-S封裝用的CoW月產僅10萬片(單價5000美

右二電競黑白圖及下列光鏡彩圖均為輝達2024 AI伺服器厚大板上所安裝4nm的H100高階

元),輝達兩項產品H100加上7nm的A100竟

繪圖晶片模塊,此項CoWoS-S封裝用CoW的月產10

萬片(單價5000美元),輝達兩項產品H100加上7nm

占了60%之多,造成AI模塊封裝的大塞車,雖

的A100竟占了60%之多,造成AI模塊封裝的大塞車

有聯電及矽品的協助仍然供不應求甚多。從所 ,

雖有聯電及矽品的協助仍然供不應求甚多。

列三圖均可看到學界業界都把矽中介層與有

從所列三圖均可看到學界業界都把矽中介層與有

機載板之間的Sn/Cu凸塊,長期誤認為是C4

機載板之間的Sn/Cu凸塊,長期誤認為是C4 Bump;

左圖最下筆者所加三彩圖,對比之下即可得知產

Bump;左圖最下筆者所加三彩圖,對比之下

線以外的專家們所知真相不多了。

即可得知產線以外的專家們所知真相不多了。

C4 高鉛

高鉛

C4 微凸塊 微凸塊 C4

矽通孔

矽中介層 矽中介層 矽中介層

CoWoS-S

此處銲 65nm 矽中介層 65nm

錫銅合 錫銅合 料是錫

此處銲

料是錫

金銲料 金銲料 銅而非

C4高鉛

銅而非

C4高鉛

此處並非

高鉛微凸塊

而另是

錫銅合金凸塊

黑色是鉛白色是錫

黑色是鉛白色是錫