Page 17 - 電路板季刊第109期

P. 17

電路板季刊 2025.10 專業技術 15

2.10 ආӻ୕܆ༀSiPၾCoWoS-Sݴື(1)

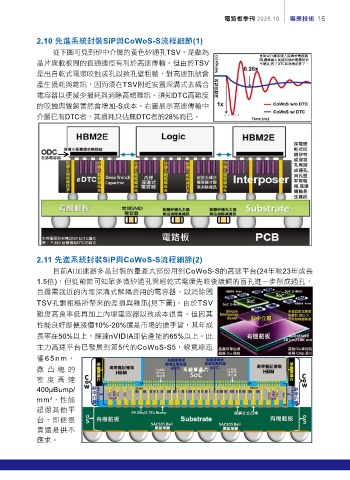

從下圖可見到矽中介層的黃色矽通孔TSV,是做為

2.11 先進系統封裝SIP與CoWoS-S流程細節(2)

系

統

先

進

封

程

細

節

裝

與

流

當矽中介層未埋入深溝式電容器

晶片與載板間的直通捷徑有利於高速傳輸。但由於TSV 時,邏輯晶片高速訊號的電壓就很

不穩定,有了DTC時就穩定多了。

從下圖可見到矽中介層的黃色矽通孔TSV,是做為晶片

是出自乾式電漿咬蝕成孔以致孔壁粗糙,對高速訊號會 訊號的壓降

與載板間的直通捷徑有利於高速傳輸。但由於TSV是出

自乾式電漿咬蝕成孔以致孔壁粗糙,對高速訊號會產生

產生損耗與雜訊,因而須在TSV附近安置深溝式去耦合

損耗與雜訊,因而須在TSV附近安置深溝式去耦合電容

電容器以便減少損耗與消除高頻雜訊。須知DTC高難度

器以便減少損耗與消除高頻雜訊。須知DTC高難度的咬

的咬蝕與鍍銅當然會增加-S成本。右圖展示高速傳輸中

蝕與鍍銅當然會增加-S成本。右圖展示高速傳輸中介層

已有DTC者,其損耗只佔無DTC者的28%而已。

介層已有DTC者,其損耗只佔無DTC者的28%而已。

有機載板

本節兩圖取材自2020 ECTC論文 電路板

集, P.380 台積電就DTC的論文

2.11 ආӻ୕܆ༀSiPၾCoWoS-Sݴື(2)

目前AI加速器多晶封裝的量產大部份用到CoWoS-S的高速平台(24年較23年成長

2.10 先進系統封裝SIP與CoWoS-S流程細節(1)

統

系

先

進

節

與

流

細

程

裝

封

1.5倍),但從前節可知眾多微矽通孔需經乾式電漿先咬後鍍銅的盲孔進一步削成通孔,

目前AI加速器的多晶封裝幾乎全都用到CoWoS-S的高速平台(24年較23年成長1.5倍),但

從前節可知眾多微小矽通孔需經乾式電漿咬成盲孔再

且還需就近的內埋深溝式解耦合用的電容器,以消除因

削成通孔,且還需就近的內埋深溝式解耦合用的電容

TSV孔銅粗糙所帶來的差損與雜訊(見下圖)。由於TSV

器,以消除因TSV孔銅粗糙所帶來的差損與雜訊(見下

圖)。由於TSV難度高良率低以致成本很貴。但因其性

難度高良率低再加上內埋電容器以致成本很貴。但因其

能良好即便漲價10%-20%還是市場的搶手貨,其年成

性能良好即便漲價10%-20%還是市場的搶手貨,其年成

長率在50%以上,輝達nVIDIA即佔產能的65%以上。此

主力高速平台已發展到第5代的CoWoS-S5,線寬線距

長率在50%以上,輝達nVIDIA即佔產能的65%以上。此

2

僅65nm,微凸塊的密度高達400μBump/mm ,性能超

主力高速平台已發展到第5代的CoWoS-S5,線寬線距

過其他平台,即便很貴還是供不應求。

僅 65n m ,

微 凸塊 的

密 度高 達

400µBump/

2

mm ,性能 6 6

超過其他平

台,即便很

貴還是供不

應求。