Page 19 - 電路板季刊第109期

P. 19

電路板季刊 2025.10 專業技術 17

2.14 ආSiPӻ୕܆ༀၾCoWoS-Sݴື(5)

從 2. 5 節左 圖可 知 2021 年 有 機載 板 上限 尺寸 約 Comp.Chip頂晶

2.14 先進SIP系統封裝與CoWoS-S流程細節(5)

與

裝

程

流

進

先

系

封

統

節

細

2

70X70mm ,但該節右上2025超大載板的面積四年中竟 2

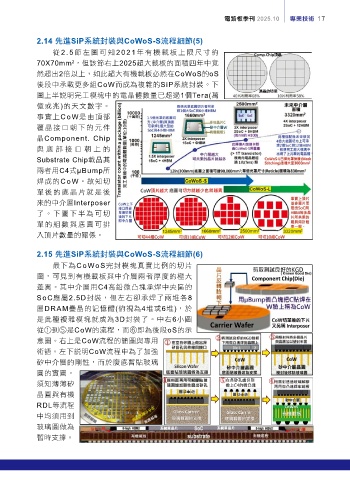

從2.5節左圖可知2021年有機載板上限尺寸約70X70mm ,

然超出2倍以上,如此超大有機載板必然在CoWoS的oS

但右上2025年的超大載板其面積四年中竟然超出2倍以上,

如此超大有機載板必然在CoWoS的oS後段中承載更多組

後段中承載更多組CoW而成為複雜的SiP系統封裝。下

CoW而成為複雜的SIP系統封裝。下圖上半說明完工模塊 頂晶的切單

圖上半說明完工模塊中的電晶體數量已超過1個Tera(萬

中的電晶體數量已超過1個Tera(萬億或兆)的天文數字。

事實上CoW是由

億或兆)的天文數字。

頂部覆晶接

事實上CoW是由頂部

口朝下的元件晶

覆晶接口朝下的元件

Compo. Chip與

底部接口朝上的

晶Component. Chip

Substrate Chip載

晶其兩者用 C4

與底部接口朝上的

式μBump所焊成

Substrate Chip載晶其

的CoW。故知切

兩者用C4式µBump所

單後的底晶片就

是後來的中介層

焊成的CoW。故知切

Interposer 了。

單後的底晶片就是後

下圖下半為可切

來的中介層Interposer

單的組數與底圓

可排入頂片數量

了。下圖下半為可切

的關係。

單的組數與底圓可排

入頂片數量的關係。

2.15 ආSiPӻ୕܆ༀၾCoWoS-Sݴື(6)

最下為CoWoS完封模塊真實比例的切片

2.15 先進SIP系統封裝與CoWoS-S流程細節(6)

先

進

程

流

裝

與

細

節

系

統

封

( Known Good Die)

圖,可見到有機載板與中介層兩者厚度的極大 Component Chip(Die)

最下為CoWoS完封模塊真實比例的切片圖,

差異。其中介層用C4高鉛微凸塊承焊中央區的

可見到有機載板與中介層兩者厚度的極大差

異。其中介層用C4高鉛微凸塊承焊中央區的

SoC應屬2.5D封裝,但左右卻承焊了兩堆各8

SoC應屬2.5D封裝,但左右卻承焊了兩堆各8

層DRAM疊晶的記憶體(俯視為4堆或6堆),於

層DRAM疊晶的記憶體(俯視為4堆或6堆) ,於

是此複雜模塊就成為3D封裝了。中右6小圖

是此種複雜模塊就成為3D封裝了。中右6小圖 CoW切單後的下片

從①到⑤是CoW的流程,而⑥即為後段oS的 Carrier Wafer 又另稱 Interposer

從①到⑤是CoW的流程,而⑥即為後段oS的示

示意圖。右上是CoW流程的簡圖與專用術語。

左下說明CoW流程中為了加強矽

意圖。右上是CoW流程的簡圖與專用

中介層的剛性,而於腹底暫貼

術語。左下說明CoW流程中為了加強

玻璃圓的實圖。須知薄薄矽晶

圓與有機RDL流程中均須用到

矽中介層的剛性,而於腹底暫貼玻璃

玻璃圓做為暫時支撐。

圓的實圖。

須知薄薄矽

晶圓與有機

RDL等流程

中均須用到

玻璃圓做為

暫時支撐。