Page 22 - 電路板季刊第109期

P. 22

20 專業技術 先進封裝與銅銅對接(2) Advanced Package

2.20 ආSiPӻ୕܆ༀCoWoS-L̨̻ٙႭ(1)

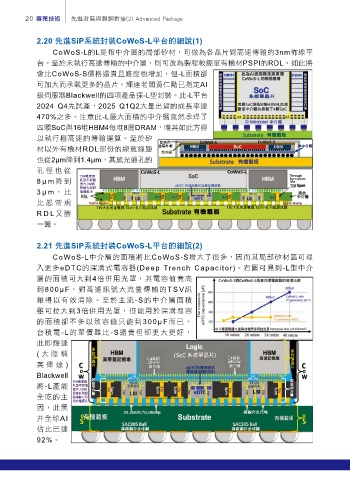

CoWoS-L的L是指中介層的局部矽材,可做為各晶片間高速傳輸的3nm佈線平

2.20 先進SiP系統封裝CoWoS-L平台的細說(1)

平

裝

台

細

的

進

先

系

封

統

說

台。至於未執行高速傳輸的中介層,則可改為製程較簡單有機材PSPI的RDL。如此將

CoWoS-L的L是指中介層局部的矽材,可做為各

會比CoWoS-S價格還貴且難度也增加,但-L面積卻

晶片間高速傳輸的3nm佈線平台。至於未執行高速

可加大而承載更多的晶片。輝達老闆黃仁勳已指定AI

傳輸的中介層,則可改為製程較簡單有機材PSPI的

RDL。如此將會比CoWoS-S價格還貴且難度也增加,

級伺服器Blackwell的四項產品採-L型封裝。此-L平台

但-L面積加大而可承載更多的晶片。輝達老闆黃仁

2024 Q4先試產,2025 Q1Q2大量出貨的成長率達

勲已指定AI級伺服器Blackwell的四項產品採-L型封

裝。此-L平台2024 Q4先試產,2025 Q1Q2已大量出

470%之多。注意此-L最大面積的中介層竟然承焊了

貨成長率達470%之多。注意此-L最大面積的中介層

四顆SoC與16堆HBM4每堆8層DRAM,唯其如此方得

竟然承焊了四顆SoC與16堆HBM4每堆8層DRAM ,

唯其如此方得以執行極高速的運算。至於矽材以外

以執行極高速的傳輸運算。至於矽

的有機材RDL部份的線寬線距 散熱用 CoWoS-S CoWoS-S

材以外有機材RDL部份的線寬線距 金屬外框 C4 C4 矽中介層

也從2μm降到1.4μm,其感光

散熱膏

通孔的孔徑也從8μm降到3μm,比

也從2µm降到1.4µm,其感光通孔的

比起常規RDL又勝一籌。

孔徑也從 CoWoS-L CoWoS-L

3μm,比起常規RDL又勝了一 Through

T TSV難度高

V

S

8µ m 降到 籌。 I V Via

孔型不好插

損大,TIV容

T

,

易做孔型好 eDTC 內埋深溝式去耦合電容器 3μm

3µ m ,比 插損較小 C4 C4 65nm 65nm C4

C4

C4

3μm TIV 3μm TIV TSV eDTC 3μm TIV TSV TSV 3μm

TIV

比起常規 Sn/Cu Bump Sn/Cu Bump

TSV

TSV

TIV大孔可走電源,TSV小孔只能走訊號 TIV大孔可走電源,TSV小孔只能走訊號

RDL 又勝

一籌。

2.21 ආSiPӻ୕܆ༀCoWoS-L̨̻ٙႭ(2)

2.21 先進SiP系統封裝CoWoS-L平台的細說(2)

系

先

細

進

的

台

說

平

統

封

裝

CoWoS-L中介層的面積將比CoWoS-S增大了很多,因而其局部矽材區可埋

入更多eDTC的深溝式電容器(Deep Trench Capacitor)。右圖可見到-L型中介

CoWoS-L中介層的面積將比CoWoS-S增大了很多,因而其局部矽材區可埋入更多eDTC的

層的面積可大到4倍併用光罩,其電容值竟高

深溝式電容器( Deep Trench Capacitor)。右

圖可見到-L型中介層的面積可大到4倍併用光

到800µ F,對高速訊號大流量傳輸的TSV訊

罩,其電容值竟高到800μF,對高速訊號大流

雜得以有效消除。至於主流-S的中介層面積

量傳輸的TSV訊雜得以有效消除。至於主流-S

雖可拉大到3倍併用光罩,但能用於深溝埋容

的中介層面積雖可拉大到3倍併用光罩,但能

用於埋容的面積卻不多以致容值只能到300μF

的面積卻不多以致容值只能到300µ F而已。

而已。-L單價雖比-S還貴但卻更大更好,此即

台積電-L的單價雖比-S還貴但卻更大更好,

輝達Blackwell將-L產能全吃的主因。

此即輝達 多枚頂晶片 多枚頂晶片

( 大陸 稱

英偉 達 ) C eDTC內埋深溝式 C

o

Blackwell W 混 混 μBump 電容器(被動元件) μBump 混 混 W

C4

C4

S

T TSV難度高 合 合 中 中 65nm 65nm 合 合

V

將-L產能 孔型不好插 介 介 主動元件 主動元件 中 中

,

V

損大,TIV容 層 層 TIV 3μm TSV TSV 3μm TIV 3μm TIV TSV eDTC 3μm TIV TSV TSV 3μm TIV 介 介 層 層

T

I

全吃的主 易做孔型好 TSV

插損較小可

用於電源孔

因,此黑

o

井全球AI S o

S

佔比已達

92%。