Page 27 - 電路板季刊第109期

P. 27

電路板季刊 2025.10 專業技術 25

2.30 IntelߠΣԶཥٙ Power Via(1)

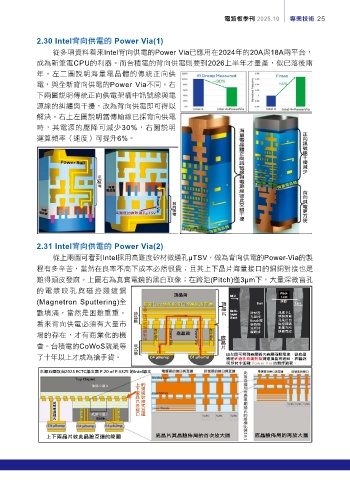

從多項資料看來Intel背向供電的Power Via已應用在2024年的20A與18A兩平台,

成為新筆電CPU的利器。而台積電的背向供電則要到2026上半年才量產,似已落後兩

2.30 Intel背向供電的 Power Via(1)

年。左二圖說明海量電晶體的傳統正向供

從多項資料看來Intel背向供電的Power Via已應

電,與全新背向供電的Power Via不同。右

用在2024年的20A與18A兩平台,成為新筆電

CUP的利器。而台積電的背向供電則要到2026

下兩圖說明傳統正向供電架構中訊號線與電

上半年才量產,似已落後兩年。左二圖說明海

源線的糾纏與干擾,改為背向供電即可得以

量電晶體的傳統正向供電,與全新背向供電的

Power Via不同。右下兩圖說明傳統正向供電

解決。右上左圖說明當傳輸線已採背向供電

架構中訊號線與電源線的糾纏與干擾,改為背

時,其電源的壓降可減少30%,右圖說明

向供電即可得以解決。右上左圖說明當傳輸線

已採背向供電時,其電源壓降可減少30%,右

運算頻率(速度)可提升6%。

圖說明運算頻率(速度)可提升6%。

高難度的微矽通孔μTSV

2.31 IntelߠΣԶཥٙ Power Via(2)

從上兩圖可看到Intel採用高難度矽材微通孔µTSV,做為背向供電的Power-Via的製

程有多辛苦,當然在良率不高下成本必然很貴;且其上下晶片海量接口的銅銅對接也是

難得頭皮發麻。上圖右為真實電鏡的黑白取像;在跨距(Pitch)僅3µm下,大量深微盲孔

的電漿咬孔與磁控濺鍍銅

頂晶背 Pitch

(Magnetron Sputtering)全 跨距1μm極多多接口的高密度互連 跨距

數填滿,當然是困難重重。 矽材盲 此處 9:1

孔是採 填銅深盲

孔是出自

看來背向供電必須有大量市 Bosch電 磁控濺鍍

漿乾蝕

法所持 多層次所

場的存在,才有商業化的機 Power Via 底晶背 Power Via 續咬成 積累而成

會。台積電的CoWoS就是等

了十年以上才成為搶手貨。 C4 μBump C4 μBump 由左圖可見到表層與次表層兩股電流,從底晶

臉經矽通孔與銅對接到達頂晶再返回。右圖說

明頂臉四接口電流最大電壓分佈也最大的畫面。

矽材中困難 Pow er Via 的製作過程。

本節五圖取自2025 ECTC論文集 P.20 of P.3325 的Intel論文

C4 μBump C4 μBump C4 μBump

上下兩晶片彼此晶臉互連的簡圖 底晶片其晶臉佈局的首次放大圖 10:1 底晶臉佈局的再放大圖