Page 28 - 電路板季刊第109期

P. 28

2.32 Intel先進封裝首秀的EMIB載板內埋晶橋

由於台積電高手CoWoS在2012年就已量產,但

卻因成本太貴、良率不高而一直處於曲高和寡的

尷尬,直到2022年才在HPC與AI的領域爆發出

26 供不應求的場面,在前車之鑒大Intel就改走低

先進封裝與銅銅對接(2) Advanced Package

專業技術

價位的EMIB,從中圖可見到載板承焊了三枚大

型晶片組,為了彼此就近溝通方便而於載板內埋

2.32 Intelආ܆ༀӸٙEMIB༱ؐʫࡽ౺

入兩個晶橋,正如同 2019年展出首樣

2.32 Intel先進封裝首秀的EMIB載板內埋晶橋

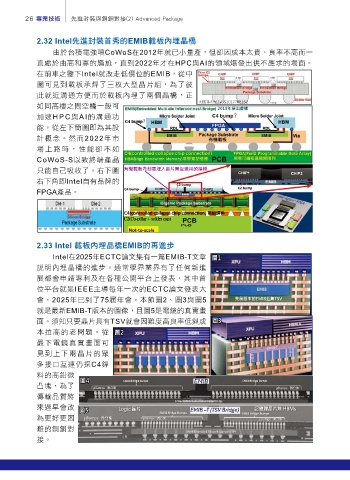

由於台積電強項CoWoS在2012年就已小量產,但卻因成本太貴、良率不高而一

高樓之間空橋一般的

由於台積電高手CoWoS在2012年就已量產,但

直處於曲高和寡的尷尬,直到2022年才在HPC與AI的領域爆發出供不應求的場面。

卻因成本太貴、良率不高而一直處於曲高和寡的

捷徑,可加速HPC與AI

在前車之鑒下Intel就改走低價位的EMIB,從中

尷尬,直到2022年才在HPC與AI的領域爆發出

的功能。從左下簡圖中

供不應求的場面,在前車之鑒大Intel就改走低

圖可見到載板承焊了三枚大型晶片組,為了彼

價位的EMIB,從中圖可見到載板承焊了三枚大

即可得知其設計的概念

此就近溝通方便而於載板內埋了兩個晶橋,正

型晶片組,為了彼此就近溝通方便而於載板內埋

。然而到了2022年實

入兩個晶橋,正如同

如同高樓之間空橋一般可 2019年展出首樣

高樓之間空橋一般的

際市場上路時,性能卻

加速HPC與AI的溝通功 k k

捷徑,可加速HPC與AI

不如CoWoS-S來得更

能。從左下簡圖即為其設

的功能。從左下簡圖中

好更快,因而終端產品

即可得知其設計的概念

計概念。然而2022年市 有機載板內刻意埋入晶片間互連用的接橋

。然而到了2022年實

只能自己吸收了。

場上路時,性能卻不如

際市場上路時,性能卻

右下圖右下角Intel自有

不如CoWoS-S來得更

CoWoS-S以致終端產品

好更快,因而終端產品

的FPGA產品。

只能自己吸收了。右下圖 有機載板內刻意埋入晶片間互連用的接橋

只能自己吸收了。

右下角即Intel自有品牌的

右下圖右下角Intel自有

的FPGA產品。

FPGA產品。

C4(controlled collapse chip connection) 高鉛銲料

l

l

2

r

a

C4(controlled collapse chip connection) 高鉛銲料

C C2(Cu-pillar + solder cap)

+

p

r

u

e

p

)

c

a

o

C

s

(

i

d

-

l

a

i

p

l

l

r

e

d

p

a

c

+

r

l

o

s

(

2

C C2(Cu-pillar + solder cap) )

-

u

C

2.33 Intel ༱ؐʫࡽ౺EMIBٙΎආӉ

2.33 Intel 載板內埋晶橋EMIB的進步

Intel在2025年ECTC論文集有一篇EMIB-T文章 圖1

Intel在2025年ECTC論文集P.269有一篇全新文章

說明內埋晶橋的進步。通常學界業界有了任何新進

EMIB-T的出現。通常學界業界有了任何新的進展

展都會申請專利及在各種公開平台上發表,其中首

都會申請專利及在各種公開平台上發表成果,其

中首位平台就是IEEE主導每年一次的ECTC論文發

位平台就是IEEE主導每年一次的ECTC論文發表大

表大會,2025年已到了75屆年會。本節圖2、圖

會,2025年已到了75屆年會。本節圖2、圖3與圖5 先前版本的EMIB並無TSV

3與圖5就是最新EMIB-T版本的圖像,且圖5是電

就是最新EMIB-T版本的圖像,且圖5是電鏡的真實畫

鏡的真實畫面。須知只要在晶片上製做TSV就會

困難度上升良率下降與成本拉高的老問題。從最

面。須知只要晶片具有TSV就會因難度高良率低與成 圖3

下電鏡真

本拉高的老問題。從 圖2

實畫面可見

到上下兩晶

最下電鏡真實畫面可

片的接口互

見到上下兩晶片的眾

連仍採C4銲

多接口互連仍採C4銲

料的μBump

料的高鉛微 圖4

凸塊,為了 μBumps 微凸塊 μBumps 微凸塊

傳輸品質將

來遲早會改 圖5 Logic 晶片 記憶體晶片堆 HBMs

為更好更困 μBumps 微凸塊 μBumps 微凸塊 μBumps 微凸塊

難的銅銅對

接。