Page 39 - 電路板季刊第107期

P. 39

電路板季刊 2025.4 專業技術 37

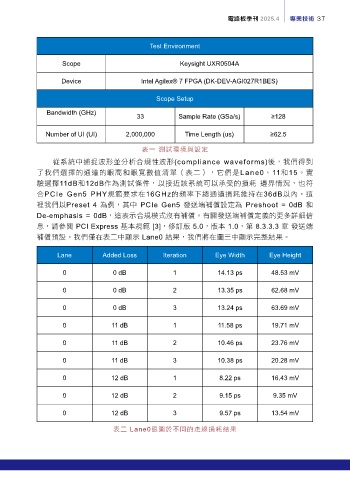

Test Environment

Scope Keysight UXR0504A

Device Intel Agilex® 7 FPGA (DK-DEV-AGI027R1BES)

Scope Setup

Bandwidth (GHz)

33 Sample Rate (GSa/s) ≥128

Number of UI (UI) 2,000,000 Time Length (us) ≥62.5

表一 測試環境與設定

從系統中捕捉波形並分析合規性波形(compliance waveforms)後,我們得到

了我們選擇的通道的眼高和眼寬數值清單(表二),它們是Lane0、11和15。實

驗選擇11dB和12dB作為測試條件,以接近該系統可以承受的損耗 邊界情況,也符

合PCIe Gen5 PHY規範要求在16GHz的頻率下總通道損耗維持在36dB以內。這

裡我們以Preset 4 為例,其中 PCIe Gen5 發送端補償設定為 Preshoot = 0dB 和

De-emphasis = 0dB,這表示合規模式沒有補償。有關發送端補償定義的更多詳細信

息,請參閱 PCI Express 基本規範 [3],修訂版 5.0,版本 1.0,第 8.3.3.3 章 發送端

補償預設。我們僅在表二中顯示 Lane0 結果,我們將在圖三中顯示完整結果。

Lane Added Loss Iteration Eye Width Eye Height

0 0 dB 1 14.13 ps 48.53 mV

0 0 dB 2 13.35 ps 62.68 mV

0 0 dB 3 13.24 ps 63.69 mV

0 11 dB 1 11.58 ps 19.71 mV

0 11 dB 2 10.46 ps 23.76 mV

0 11 dB 3 10.38 ps 20.28 mV

0 12 dB 1 8.22 ps 16.43 mV

0 12 dB 2 9.15 ps 9.35 mV

0 12 dB 3 9.57 ps 13.54 mV

表二 Lane0眼圖於不同的走線損耗結果